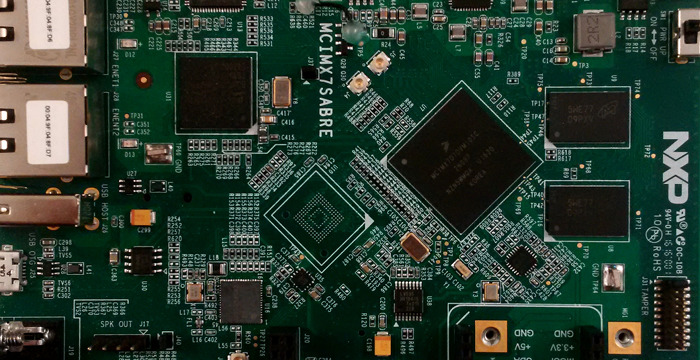

i.MX7D M4 Bare-Metal Bring-up and Benchmark

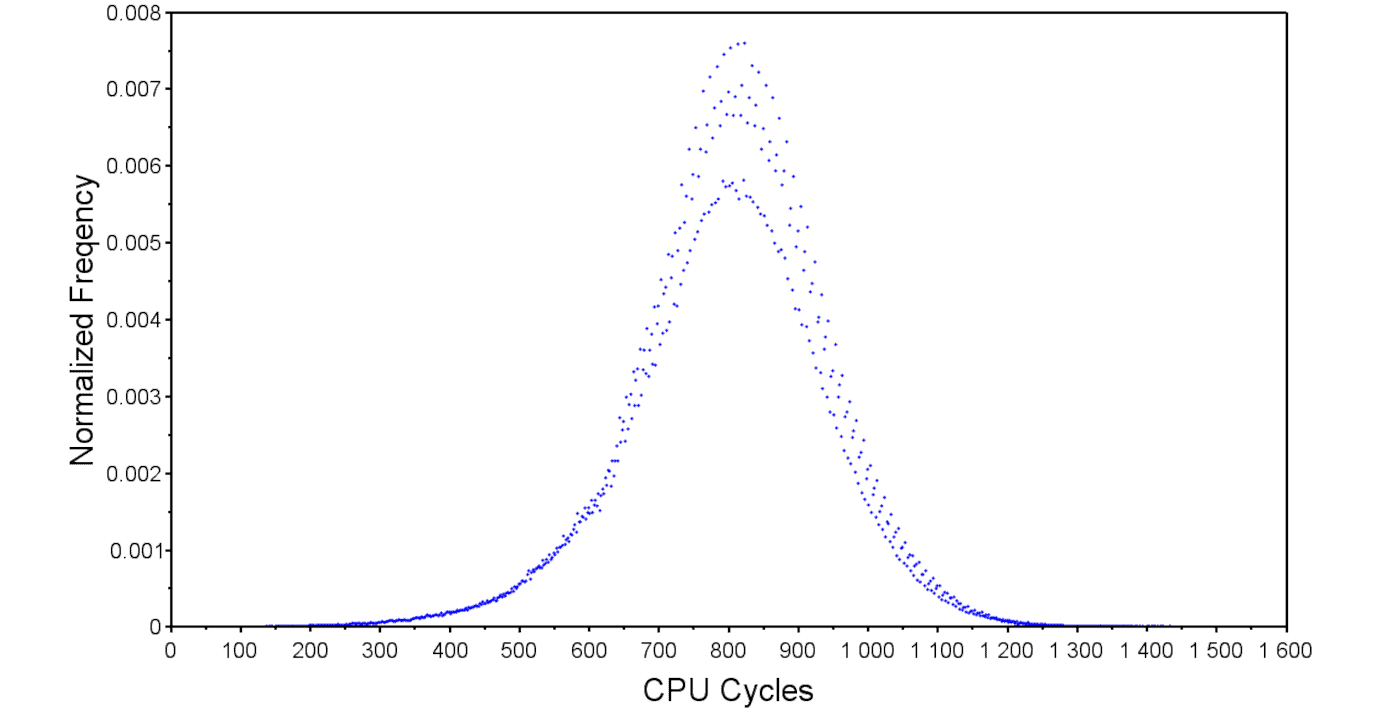

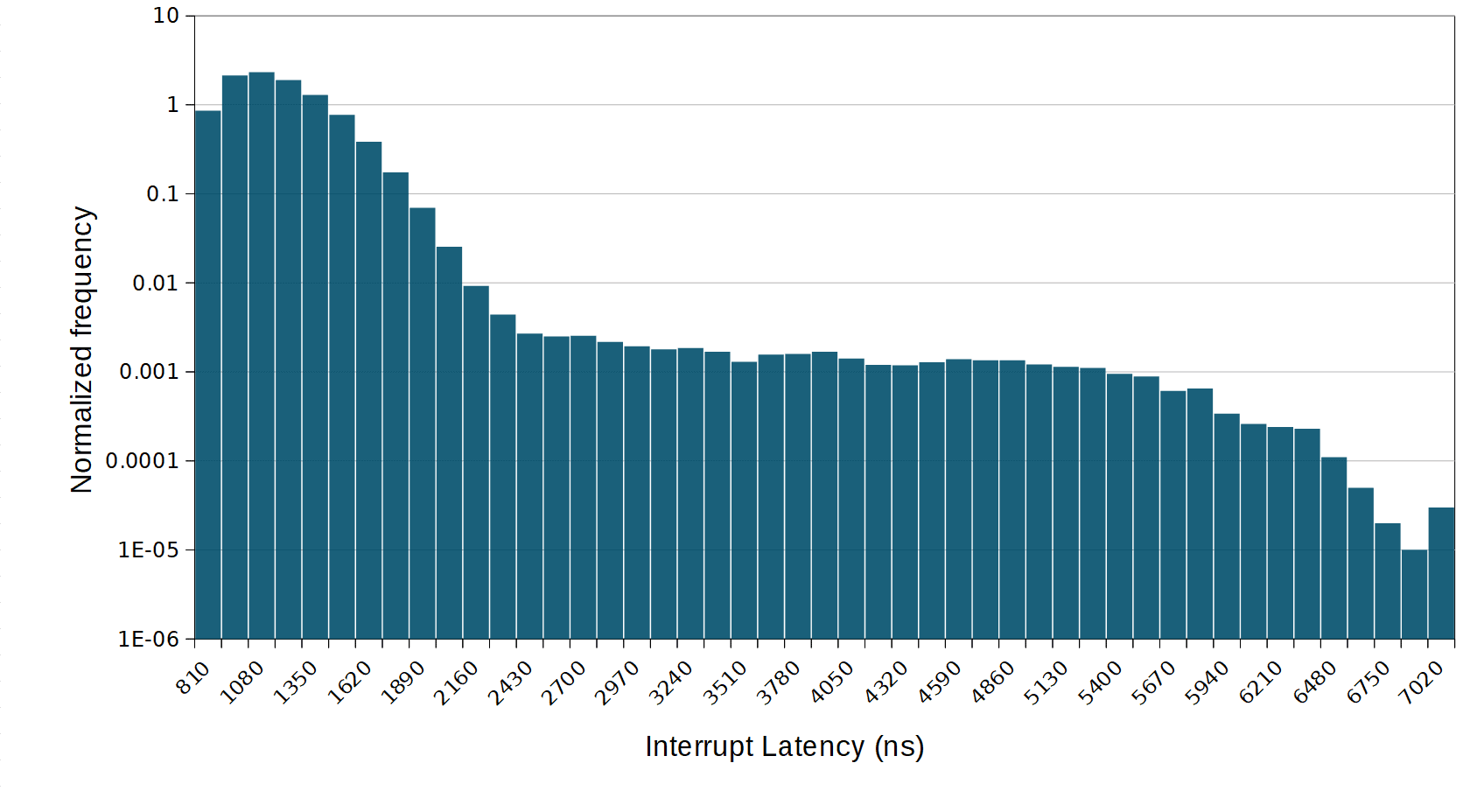

Following up on the last piece about the NXP i.MX 7, this article looks at the ARM Cortex-M4 companion of the Cortex-A7 present in the i.MX 7. Or to put it another way, a Kinetis-on-chip since it’s very similar to a high-end Cortex-M4 based Kinetis. This article summarizes my experience writing a brand new bare