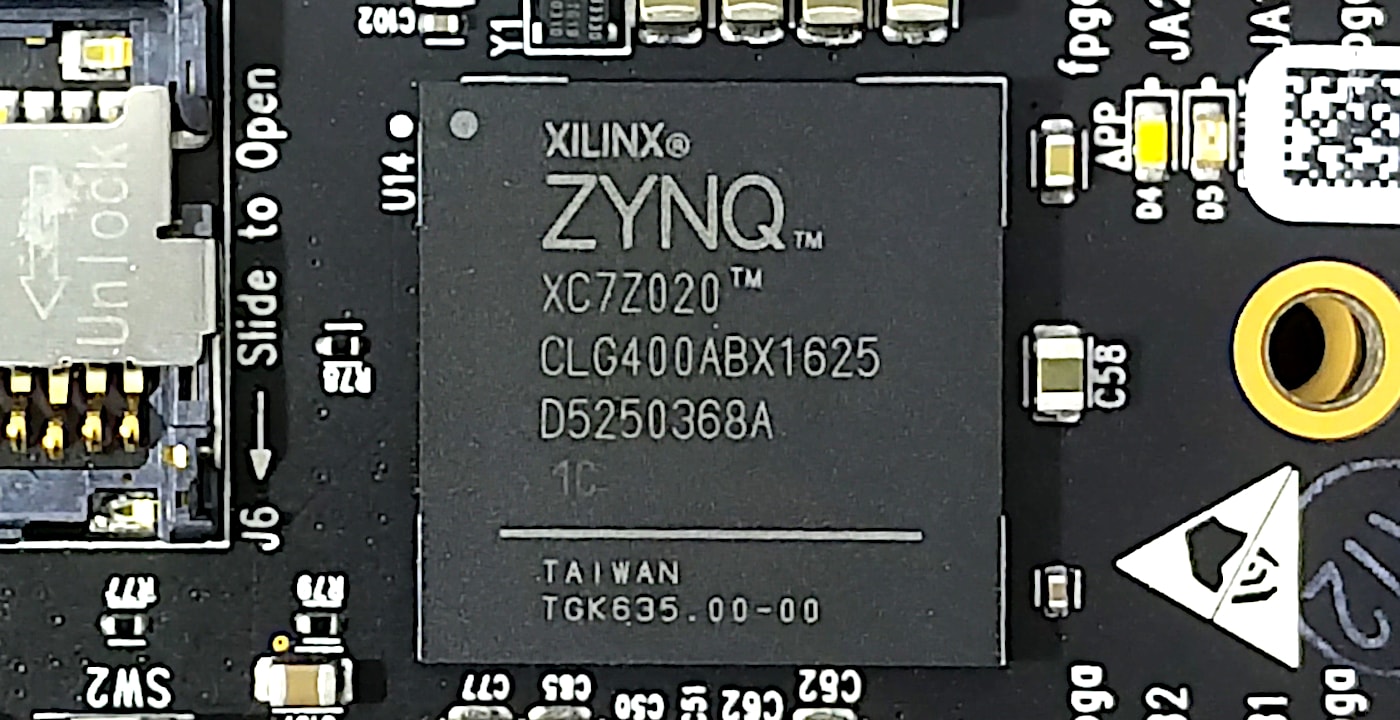

Zynq-7000 Bare-Metal Benchmarks

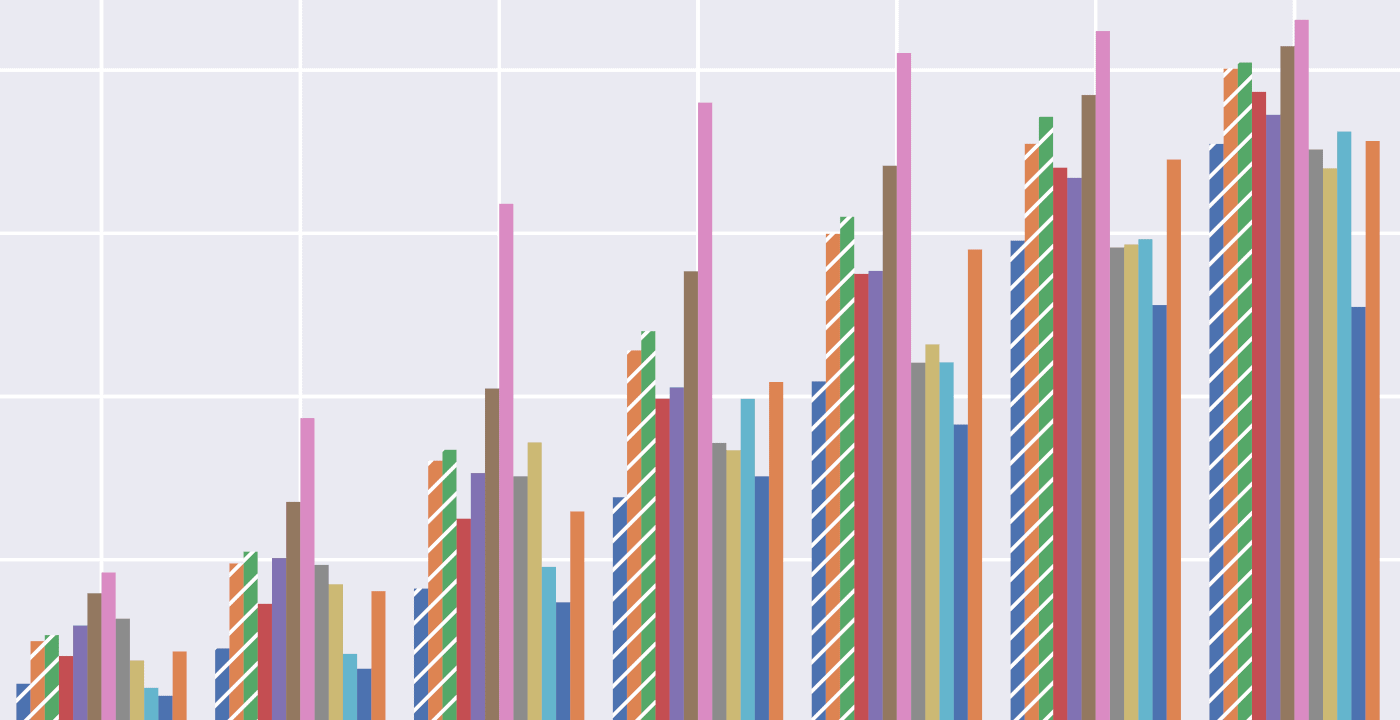

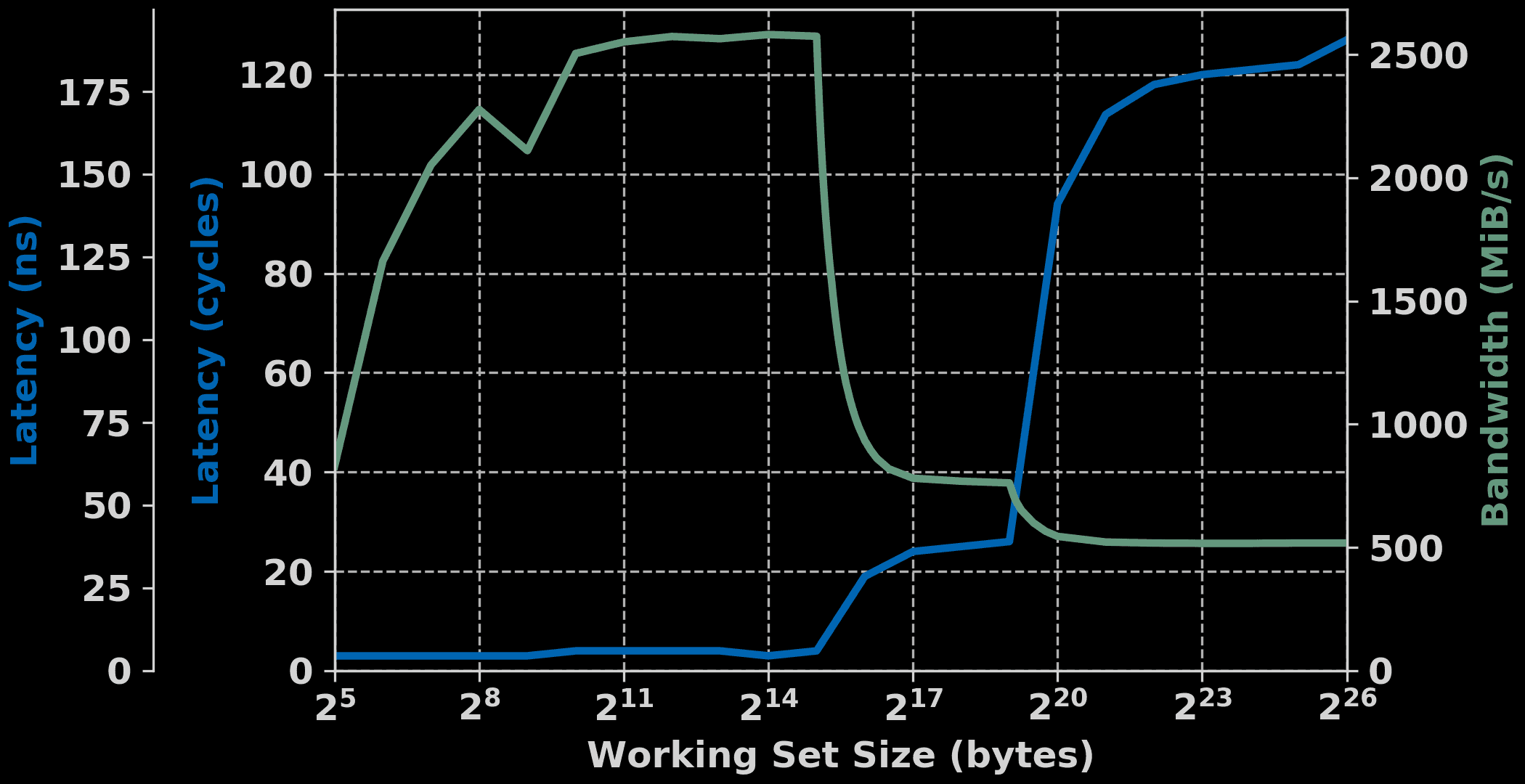

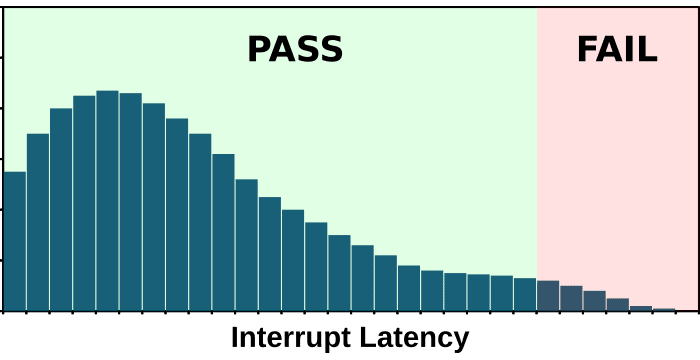

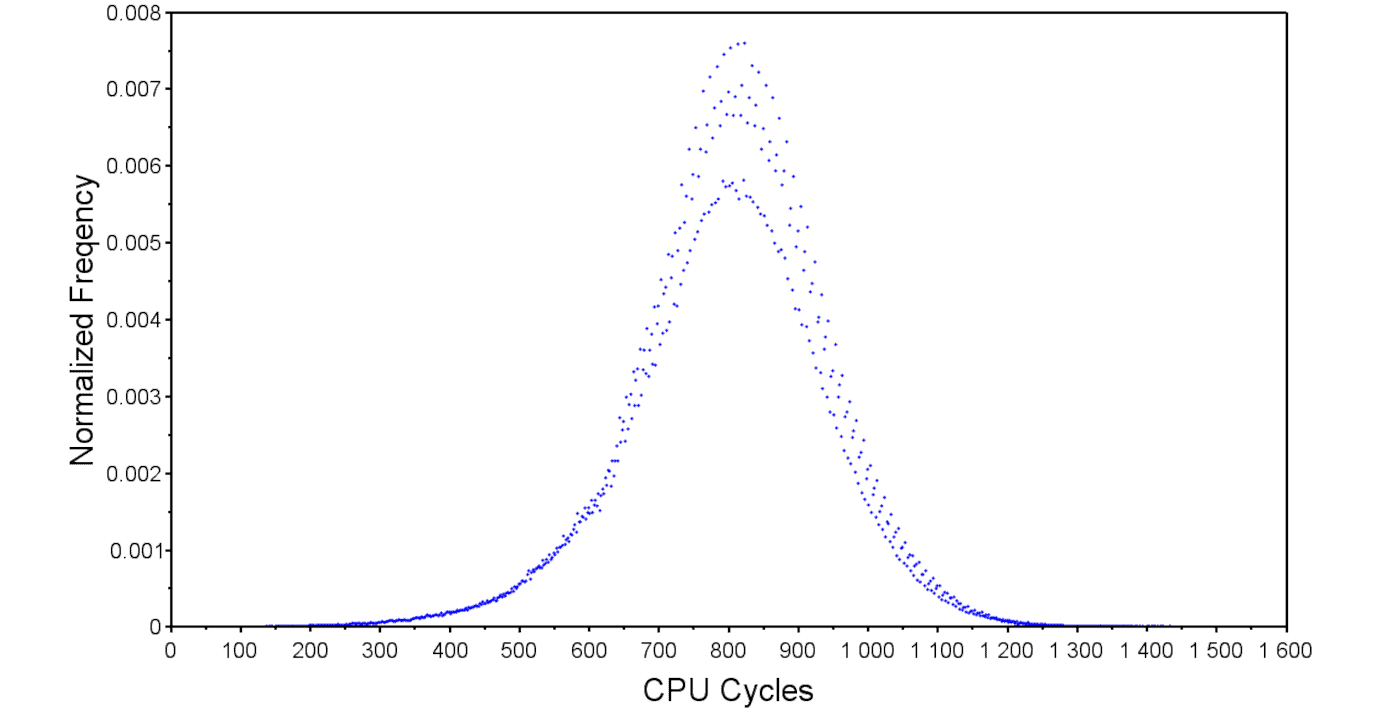

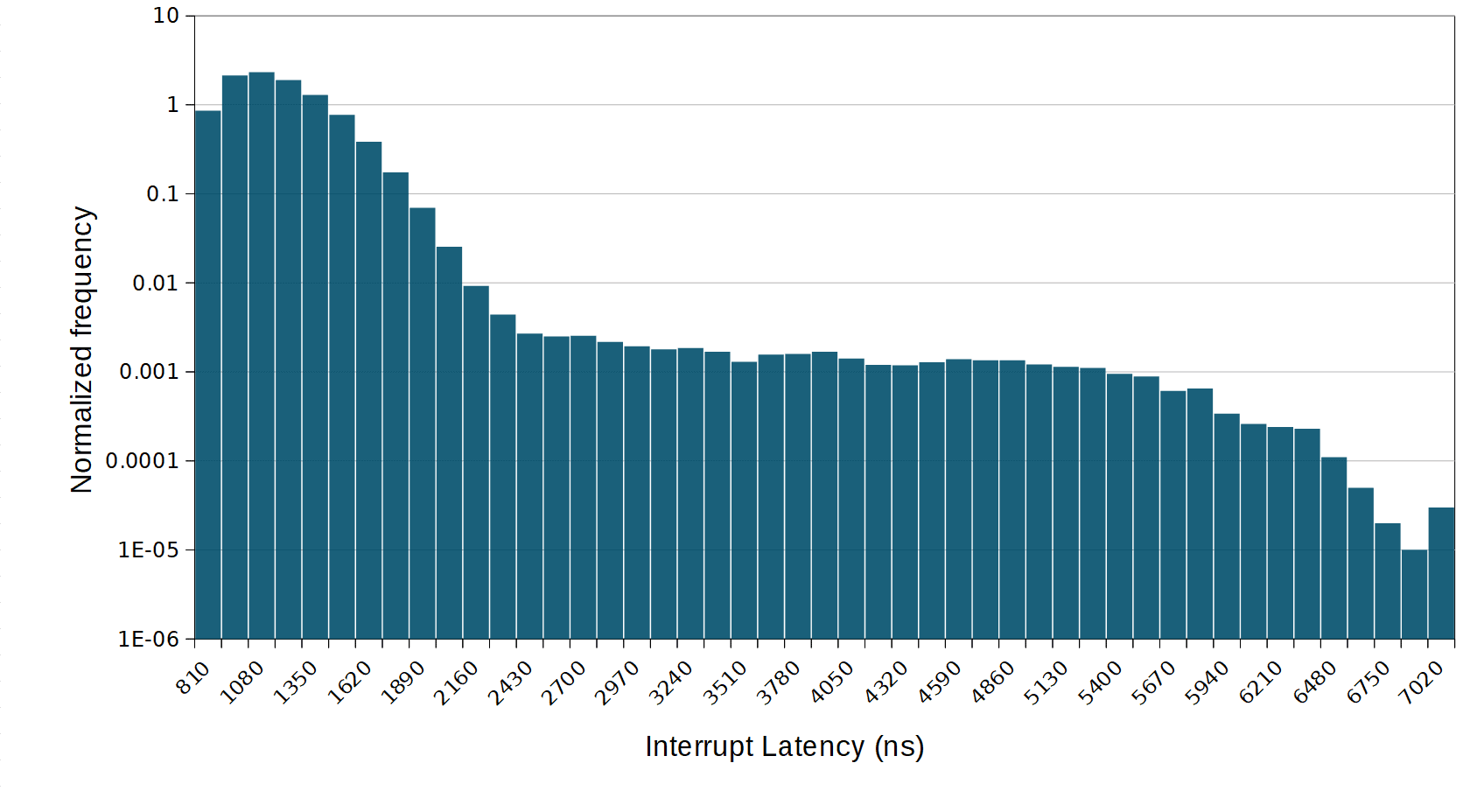

In this article we’ll look at some well-known CPU benchmarks, namely CoreMARK, Dhrystone, Whetstone and Linpack. Following that, we’ll look at the memory bandwidth and latency of the external DDR memory, On-Chip RAM and block RAM (BRAM) in the FPGA. Finally, we’ll round up with numbers on interrupt latency.